# Intel® Atom<sup>™</sup> Processor D2000 and N2000 Series

Datasheet - Volume 1 of 2

Refer to Doc ID 326137-003 for Volume 2 of 2 July 2012 Revision 003

Document Number: 326136-003

INFORMATION IN THIS DOCUMENT IS PROVIDED IN CONNECTION WITH INTEL® PRODUCTS. NO LICENSE, EXPRESS OR IMPLIED, BY ESTOPPEL OR OTHERWISE, TO ANY INTELLECTUAL PROPERTY RIGHTS IS GRANTED BY THIS DOCUMENT. EXCEPT AS PROVIDED IN INTEL'S TERMS AND CONDITIONS OF SALE FOR SUCH PRODUCTS, INTEL ASSUMES NO LIABILITY WHATSOEVER, AND INTEL DISCLAIMS ANY EXPRESS OR IMPLIED WARRANTY, RELATING TO SALE AND/OR USE OF INTEL PRODUCTS INCLUDING LIABILITY OR WARRANTIES RELATING TO FITNESS FOR A PARTICULAR PURPOSE, MERCHANTABILITY, OR INFRINGEMENT OF ANY PATENT, COPYRIGHT OR OTHER INTELLECTUAL PROPERTY RIGHT.

UNLESS OTHERWISE AGREED IN WRITING BY INTEL, THE INTEL PRODUCTS ARE NOT DESIGNED NOR INTENDED FOR ANY APPLICATION IN WHICH THE FAILURE OF THE INTEL PRODUCT COULD CREATE A SITUATION WHERE PERSONAL INJURY OR DEATH MAY OCCUR.

Intel may make changes to specifications and product descriptions at any time, without notice. Designers must not rely on the absence or characteristics of any features or instructions marked "reserved" or "undefined." Intel reserves these for future definition and shall have no responsibility whatsoever for conflicts or incompatibilities arising from future changes to them. The information here is subject to change without notice. Do not finalize a design with this information.

The products described in this document may contain design defects or errors known as errata which may cause the product to deviate from published specifications. Current characterized errata are available on request.

Intel<sup>®</sup> 64 requires a computer system with a processor, chipset, BIOS, operating system, device drivers, and applications enabled for Intel 64. Processor will not operate (including 32-bit operation) without an Intel 64-enabled BIOS. Performance will vary depending on your hardware and software configurations. See http://www.intel.com/technology/intel64/index.htm for more information including details on which processors support Intel 64, or consult with your system vendor for more information.

Hyper-Threading Technology requires a computer system with a processor supporting Hyper-Threading Technology and HT Technology enabled chipset, BIOS and operating system. Performance will vary depending on the specific hardware and software you see. See http://www.intel.com/technology/hypertheading/ for more information including details on which processor supports HT Technology.

Intel processor numbers are not a measure of performance. Processor numbers differentiate features within each processor family, not across different processor families. Click here for details.

Intel, Intel Atom and the Intel logo are trademarks or registered trademarks of Intel Corporation or its subsidiaries in the U.S. and other countries.

\*Other names and brands may be claimed as the property of others.

Copyright © 2012 Intel Corporation. All rights reserved.

## **Contents**

| 1 | Intro  | duction                                                                   | 9  |

|---|--------|---------------------------------------------------------------------------|----|

|   | 1.1    | Intel® Atom <sup>™</sup> Processor D2000 Series and N2000 Series Features | .9 |

|   | 1.2    | System Memory Features                                                    |    |

|   | 1.3    | Direct Media Interface Features                                           |    |

|   | 1.4    | Graphics Processing Unit Features                                         |    |

|   | 1.5    | Video                                                                     |    |

|   | 1.6    | Clocking                                                                  |    |

|   | 1.7    | Power Management                                                          |    |

|   |        | 1.7.1 Terminology                                                         |    |

|   | 1.8    | References                                                                |    |

|   | 1.9    | System Block Diagram                                                      |    |

|   |        | 1.9.1 PHOLD limitation on Legacy Feature                                  | 16 |

| 2 | Signa  | I Description                                                             | 17 |

|   | 2.1    | CPU Legacy Signal                                                         | 18 |

|   | 2.2    | System Memory Interface                                                   |    |

|   | 2.3    | DMI - Direct Media Interface                                              |    |

|   | 2.4    | PLL Signals                                                               | 23 |

|   | 2.5    | Analog Display Signals                                                    | 23 |

|   | 2.6    | LVDS Signals                                                              |    |

|   | 2.7    | DDI Audio Interface                                                       | 25 |

|   | 2.8    | DDI Port 0                                                                |    |

|   | 2.9    | DDI Port1                                                                 |    |

|   | 2.10   | JTAG/ITP Signals                                                          |    |

|   | 2.11   | Error and Thermal Protection                                              |    |

|   | 2.12   | Processor Core Power Signals                                              |    |

|   | 2.13   | Graphics, DMI and Memory Core Power Signals                               |    |

|   | 2.14   | Ground                                                                    | 31 |

| 3 | Funct  | ional Description                                                         | 32 |

|   | 3.1    | System Memory Controller                                                  | 32 |

|   | -      | 3.1.1 System Memory Organization Modes                                    |    |

|   |        | 3.1.2 System Memory Technology Supported                                  |    |

|   |        | 3.1.3 Rules for populating DIMM Slots                                     | 34 |

|   | 3.2    | Graphics Processing Unit                                                  |    |

|   |        | 3.2.1 3-D Core Key Features                                               | 34 |

|   |        | 3.2.2 2D Engine                                                           |    |

|   |        | 3.2.3 Analog Display Port Characteristics                                 |    |

|   |        | 3.2.4 Digital Display Interfaces                                          |    |

|   |        | 3.2.5 Multiple Display Configurations                                     | 46 |

|   | 3.3    | Thermal Sensor                                                            |    |

|   |        | 3.3.1 PCI Device 0, Function 0                                            |    |

|   | 3.4    | Power Management                                                          |    |

|   |        | 3.4.1 Interface Power States Supported                                    | 47 |

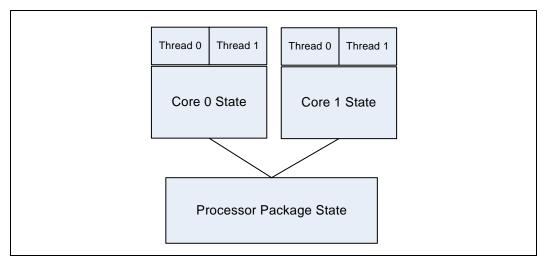

|   |        | 3.4.2 Intel® Hyper-Threading Technology                                   | 47 |

| 4 | Electi | rical Specifications                                                      | 48 |

|   | 4.1    | Power and Ground Balls                                                    |    |

|   | 4.2    | Decoupling Guidelines                                                     |    |

|   |        | 4.2.1 Voltage Rail Decoupling                                             |    |

|   |        | · ····································                                    |    |

|   | 4.3   | Process  | sor Clocking49                                    |

|---|-------|----------|---------------------------------------------------|

|   |       | 4.3.1    | PLL Power Supply49                                |

|   | 4.4   |          | e Identification (VID)50                          |

|   | 4.5   |          | ophic Thermal Protection56                        |

|   | 4.6   |          | ed or Unused Signals                              |

|   | 4.7   |          | Groups                                            |

|   | 4.8   |          | ccess Port (TAP) Connection57                     |

|   | 4.9   | DC Spe   | cifications57                                     |

|   |       | 4.9.1    | Flexible Motherboard Guidelines (FMB)57           |

|   |       | 4.9.2    | Voltage and Current Specifications58              |

|   |       | 4.9.3    | DC Specifications64                               |

| 5 | Mech  | anical S | Specifications and Ball Information74             |

|   | 5.1   |          | nical Specifications                              |

|   |       | 5.1.1    | Mechanical Drawings                               |

|   |       | 5.1.2    | Loading Specifications                            |

|   | 5.2   |          | sor Ballout Assignment                            |

|   |       |          | -                                                 |

| 6 | -     |          | ty Specifications                                 |

|   | 6.1   |          | Quality Specifications and Measurement Guidelines |

|   |       | 6.1.1    | Overshoot/Undershoot Guidelines                   |

|   |       | 6.1.2    | Overshoot/Undershoot Magnitude                    |

|   |       | 6.1.3    | Overshoot/Undershoot Pulse Duration95             |

| 7 | Powe  | er Mana  | gement97                                          |

|   | 7.1   | ACPI st  | ate Supported                                     |

|   |       | 7.1.1    | System States                                     |

|   |       | 7.1.2    | Processor Idle States                             |

|   |       | 7.1.3    | Integrated Graphics Display States98              |

|   |       | 7.1.4    | Integrated Memory Controller States               |

|   |       | 7.1.5    | DMI States                                        |

|   |       | 7.1.6    | Interface State Combinations                      |

|   | 7.2   | Process  | sor Core Power Management                         |

|   |       | 7.2.1    | Enhanced Intel SpeedStep® Technology100           |

|   |       | 7.2.2    | Dynamic Cache Sizing100                           |

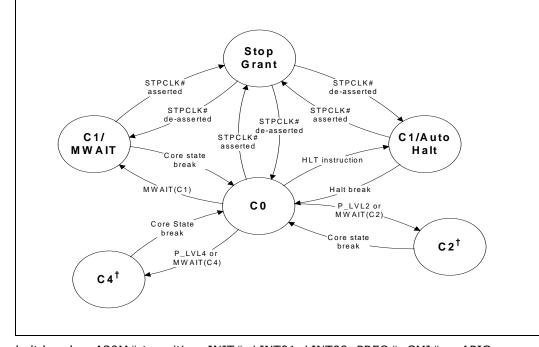

|   |       | 7.2.3    | Low-Power Idle States101                          |

|   |       | 7.2.4    | Graphics Power Management103                      |

|   |       | 7.2.5    | Thread C-state Description105                     |

|   |       | 7.2.6    | Processor Core/ C-states Description106           |

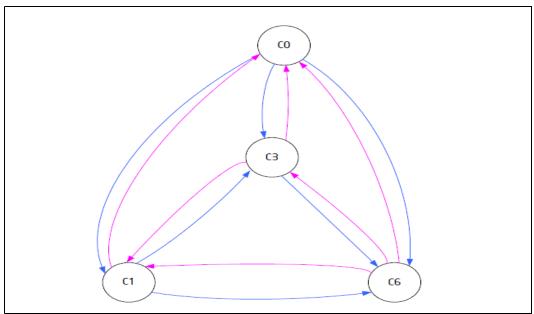

|   |       | 7.2.7    | Package C-States107                               |

|   | 7.3   |          | wer Management110                                 |

|   |       | 7.3.1    | Disabling Unused System Memory Outputs110         |

|   |       | 7.3.2    | DRAM Power Management and Initialization111       |

|   | 7.4   |          | wer Management                                    |

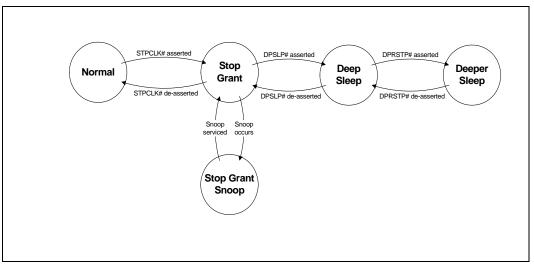

|   |       | 7.4.1    | Stop-Grant State                                  |

|   |       | 7.4.2    | Stop-Grant Snoop State                            |

|   |       | 7.4.3    | Deep Sleep State                                  |

|   |       | 7.4.4    | Deeper Sleep State                                |

|   |       | 7.4.5    | Extended Low-Power States                         |

| 8 | Therr | nal Spe  | cifications and Design Considerations115          |

|   | 8.1   | Therma   | al Specifications                                 |

|   |       | 8.1.1    | Intel® Thermal Monitor                            |

|   |       | 8.1.2    | Digital Thermal Sensor                            |

|   |       | 8.1.3    | Out of Specification Detection                    |

|   |       |          |                                                   |

|    | 8.1.4 PROCHOT# Signal Pin        | 119 |

|----|----------------------------------|-----|

| 9  | Testability                      | 120 |

|    | 9.1 JTAG Boundary Scan           | 120 |

|    | 9.2 TAP Instructions and Opcodes |     |

| 10 | Debug Tool Specifications        | 122 |

#### **Figures**

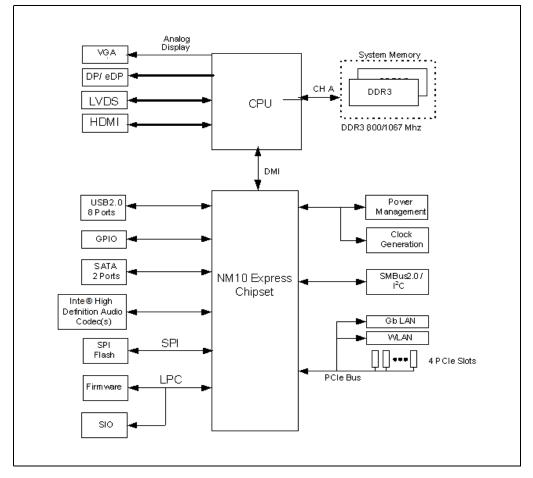

| 1-1 Intel® Atom <sup>™</sup> D2000 series/N2000 series System Block Diagram  |     |

|------------------------------------------------------------------------------|-----|

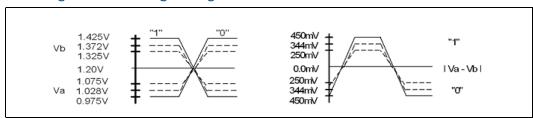

| 3-2 LVDS Signals and Swing Voltage                                           | 40  |

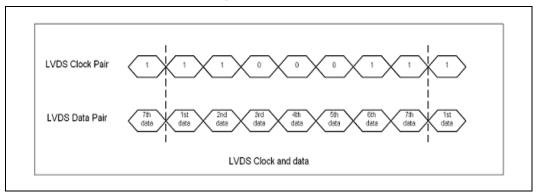

| 3-3 LVDS Clock and Data Relationship                                         |     |

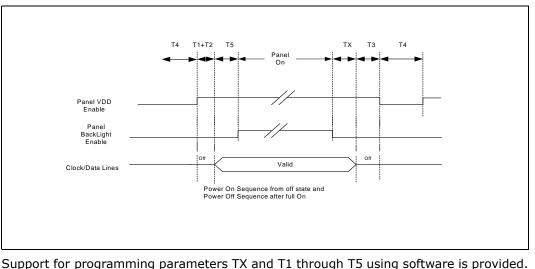

| 3-4 Panel Power Sequencing                                                   |     |

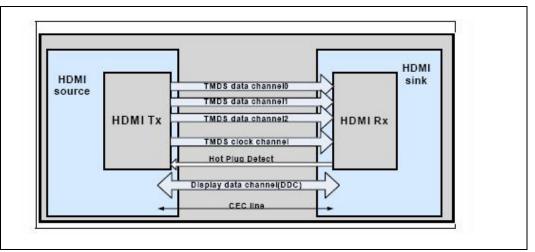

| 3-5 HDMI Overview                                                            |     |

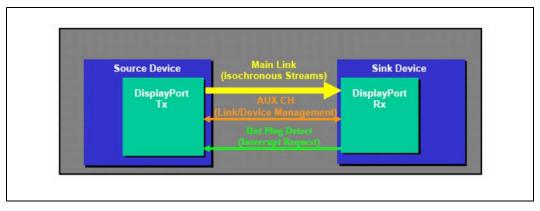

| 3-6 DP Overview                                                              |     |

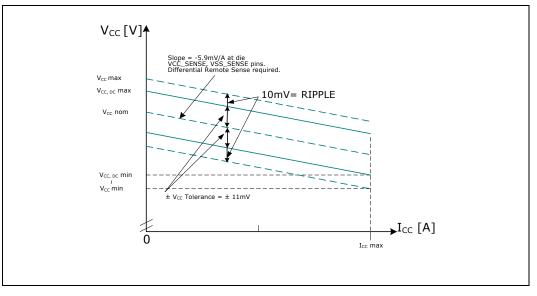

| 4-7 Vcc and Icc Processor Loadline                                           |     |

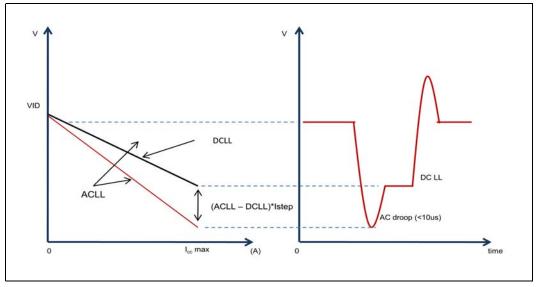

| 4-8 Vcc AC Vs. DC Loadline                                                   |     |

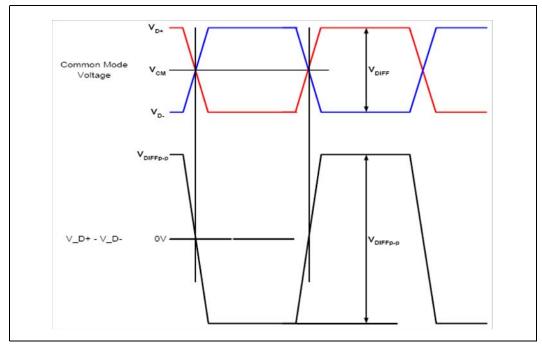

| 4-9 Definition of Differential Voltage and Differential Voltage Peak-to-Peak |     |

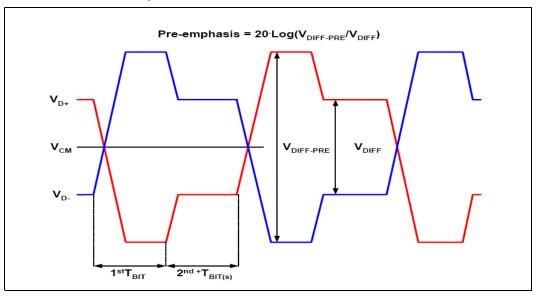

| 4-10Definition of Pre-emphasis                                               | 72  |

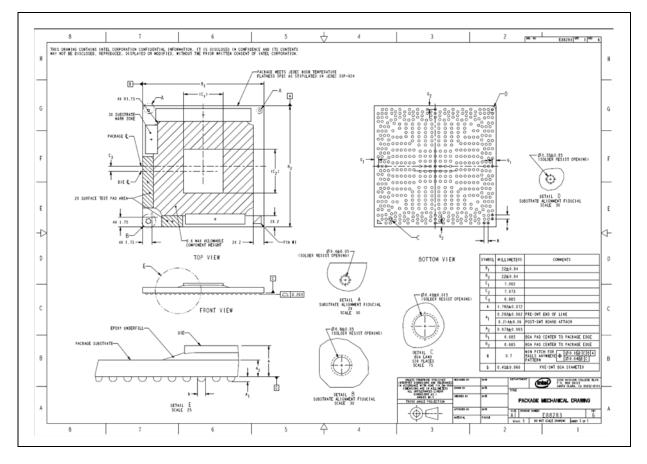

| 5-11 Mechanical Drawings                                                     |     |

| 5-12 Pinmap (Top View, Upper-Left Quadrant)                                  |     |

| 5-13 Pinmap (Top View, Upper-Right Quadrant)                                 |     |

| 5-14 Pinmap (Top View, Lower-Left Quadrant)                                  |     |

| 5-15Pinmap (Top View, Lower-Right Quadrant)                                  |     |

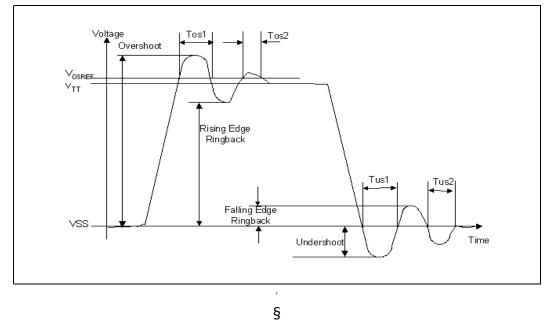

| 6-16Overshoot, Undershoot, and Ringback Illustration                         |     |

| 7-17Idle Power Management Breakdown of the Processor Cores                   |     |

| 7-18Thread and Core C-state Entry and Exit                                   | 102 |

| 7-19Processor Core Low-Power States                                          |     |

| 7-20Package C-state Entry and Exit                                           |     |

| 9-21JTAG Boundary Scan Test Mode Initialization Cycles                       | 120 |

| · · ·                                                                        |     |

#### **Tables**

| 1-1 Summary of the Resolution of Graphic interface                 | 12 |

|--------------------------------------------------------------------|----|

| 1-2 The Display core clock Frequency by Skus                       |    |

| 1-3 27 MHz Requirement Range                                       | 13 |

| 2-4 Signal Type                                                    | 17 |

| 2-5 Signal Description Buffer Types                                | 17 |

| 2-6 CPU Legacy Signal                                              | 18 |

| 2-7 Memory Channel A                                               | 20 |

| 2-8 Memory Reference and Compensation                              | 21 |

| 2-9 Reset and Miscellaneous Signal                                 |    |

| 2-10DMI - Processor to Intel NM10 Express Chipset Serial Interface | 22 |

| 2-11PLL Signals                                                    | 23 |

| 2-12Analog Display Signals                                         |    |

| 2-13LVDS Signals                                                   | 24 |

| 2-14DDI Audio Signals                                              |    |

| 2-15DDI Port 0                                                     | 27 |

| 2-16DDI Port 1                                                     | 28 |

| 2-17JTAG/ITP Signals                                               | 28 |

| 2-18Error and Thermal Protection                                   | 29 |

| 2-19Processor Core Power Signals                                   | 29 |

| 2-20Power Signals                                                  | 30 |

| 2-21Ground                                                         | 31 |

| 3-22Support DRAM Devices                                                               | 33  |

|----------------------------------------------------------------------------------------|-----|

| 3-23Supported Memory Size Per Rank                                                     | 33  |

| 3-24Support Memory Configurations                                                      | 33  |

| 3-25Analog Port Characteristics                                                        |     |

| 3-26Panel Power Sequence Timing Parameters                                             | 42  |

| 3-27Main Memory States                                                                 |     |

| 4-28PLL Reference Clock                                                                |     |

| 4-29VRD 12.0 Voltage Identification Definition                                         | 50  |

| 4-30Processor Core Active and Idle Mode DC Voltage and Current Specifications          | 58  |

| 4-31Istep                                                                              |     |

| 4-32Processor Uncore I/O Buffer Supply DC Voltage and Current Specifications           |     |

| 4-33Input Clocks (BCLK, HPL_CLKIN, DPL_REFCLKIN, EXP_CLKIN) Differential Specification | 64  |

| 4-34DDR3/DDR3L Signal Group DC Specifications                                          |     |

| 4-35CPU Sideband CMOS Signal Group DC Specification                                    |     |

| 4-36CPU Sideband OD 25 Ohm 1.05 V Signal Group DC Specification                        |     |

| 4-37CPU Sideband OD 12.5 Ohms 1.05 V Signal Group DC Specification                     |     |

| 4-38CPU Sideband OD 1.8 V Signal Group DC Specification                                |     |

| 4-393.3-V DC Specification                                                             |     |

| 4-401.5-V DC specification                                                             |     |

| 4-41High Voltage GPIO CMOS Signal DC Specification                                     |     |

| 4-42R,G,B/CRT DAC Display DC specification (Functional Operating Range)                | 68  |

| 4-43High Voltage GPIO OD Signal DC Specification                                       |     |

| 4-44CRT_HSYNC and CRT_VSYNC DC Specification                                           | 69  |

| 4-45LVDS Interface DC Specification (Functional Operating Range,                       | ~ ~ |

| $VCCLVDS = 1.8 V \pm 5\%$ ).                                                           | 69  |

| 4-46DDI Main Transmitter DC Specification                                              |     |

| 4-47DDI AUX Channel DC Specification                                                   |     |

| 4-48DMI Receiver DC specification                                                      |     |

| 5-49Processor Ball list by Ball Name                                                   |     |

| 6-50Input Signal Group Ringback Duration Specification                                 |     |

| 7-51System States                                                                      |     |

| 7-52Processor Core/ States Support                                                     |     |

| 7-53Integrated Graphics Display Device Control                                         |     |

| 7-54Main Memory States                                                                 |     |

| 7-55DMI States                                                                         |     |

| 7-56G, S and C State combinations                                                      |     |

| 7-57D, S and C state Combinations                                                      |     |

| 7-58Coordination of Thread Low-power States at the /Core Level                         |     |

| 7-59Coordination of Core Power States at the package Level                             |     |

| 8-60Power Specifications for the Standard Voltage Processor (Updated)                  |     |

| 9-61Supported TAP Instructions                                                         | 121 |

## **Revision History**

| Revision<br>Number | Description                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                |                |

|--------------------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|----------------|

| 001                | Initial Release                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            | September 2011 |

| 002                | <ul> <li>Chapter 1</li> <li>Section 1.2 <ul> <li>Added the DDR3L feature with Next Generation Intel® Atom™ Processor based Mobile Platform CPU.</li> <li>Updated the Raw Card support type for DDR3 and DDR3L.</li> </ul> </li> <li>Section 1.4- Added Next Generation Intel® Atom™ Processor based (Desktop and Mobile) Platform SKU model.</li> <li>Section 1.5- Added the Next Generation Intel® Atom™ Processor based (Desktop and Mobile) Platform SKU model.</li> <li>Table 1-2- Added D2550 core clock frequency.</li> <li>Section 1.7.1- Added DDR3L Terminology.</li> </ul> Chapter 2 <ul> <li>Table 2-5- Updated DDR3 buffer voltage with 1.35 V.</li> <li>Table 2-8- Added the signal description of DDR3_DRAMRST#.</li> <li>Table 2-20- Added the voltage of V_SM and VCCCKDDR with 1.35 V when implementing DDR3L.</li> </ul> Chapter 3 <ul> <li>Section 3.1</li> <li>Added the DDR3L features with Next Generation Intel® Atom™ Processor based Mobile Platform CPU.</li> <li>Added the DDR3L features with Next Generation Intel® Atom™ Processor based Mobile Platform CPU.</li> <li>Added the DDR3L features with Next Generation Intel® Atom™ Processor based Mobile Platform SKU model in Parameter Column.</li> </ul> Chapter 4 <ul> <li>Table 4-30- Added Next Generation Intel® Atom™ Processor based (Desktop and Mobile) Platform SKU model in Parameter Column. <ul> <li>Table 4-32</li> <li>Updated VCCGFX voltage.</li> <li>Added the max/min voltage of V_SM and VCCCKDDR when implementing DDR3L.</li> <li>Added the max/min voltage of V_SM and VCCCKDDR when implementing DDR3L.</li> <li>Added the max/min voltage of V_SM and VCCCKDDR when implementing DDR3L.</li> </ul> Added the max/min voltage of V_SM and VCCCKDDR when implementing DDR3L. <ul> <li>Table 4-34- Added the max input leakage current value when implementing DDR3L.</li> <li>Table 4-34- Added the max value of LSB current.</li> </ul> Chapter 8 <ul> <li>Table 8-60- Updated new Next Generation Intel® Atom™ Processor based (Desktop and Mobile) Platform SKU with CPU fre</li></ul></li></ul> | December 2011  |

| Revision<br>Number | Description                                                                                                                                                                                                                                      | Date      |

|--------------------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-----------|

|                    | Chapter 1                                                                                                                                                                                                                                        |           |

|                    | • Section 1.2 - Removed 512 MB from Supported total max memory size.<br>Removed 4 Gbit from Supported max densities. Added raw card support<br>type for memory down design.                                                                      |           |

|                    | <ul> <li>Section 1.4- Removed DX*10 support</li> </ul>                                                                                                                                                                                           |           |

|                    | • Section 1.5- Changed the Hardware Decode support description. It is now for Adobe 11.0 and newer versions.                                                                                                                                     |           |

|                    | • Section 1.8 - Updated reference document number in the table.                                                                                                                                                                                  |           |

|                    | Chapter 2                                                                                                                                                                                                                                        | July 2012 |

|                    | <ul> <li>Table 2-9 - Removed RSVD_NCTF_* and XDP_RSVD_[17:0]</li> </ul>                                                                                                                                                                          |           |

| 003                | • Table 2-12 - Modified DAC_IRFEF resistor value from 680 Ohm to 649 Ohm. Changed DAC_IREF signal name to CRT_IREF.                                                                                                                              |           |

|                    | Table 2-20 - Added VCC_GFX for N2000 series                                                                                                                                                                                                      |           |

|                    | Chapter 3                                                                                                                                                                                                                                        |           |

|                    | Section 3.1- Removed SO-DIMM only                                                                                                                                                                                                                |           |

|                    | • Section 3.1.2- Added raw card support type for memory down design                                                                                                                                                                              |           |

|                    | <ul> <li>Section 3.2.4.8- Updated the states that the Display Port audio does<br/>not support</li> </ul>                                                                                                                                         |           |

|                    | Chapter 4                                                                                                                                                                                                                                        |           |

|                    | • Table 4-32 - For D2000 series, separated VCCRAMXXX from other 1.067 V power rails and created a new row for it; also reversed other 1.067 V values back to 1.05 V. The voltage requirements of VCCRAMXXX for different CPUs are different now. |           |

§

## 1 Introduction

This Datasheet (DS) provides Direct Current (DC) and Alternate Current (AC) electrical specifications, signal integrity, differential signaling specifications, pinout and signal definitions, interface functional descriptions, and additional feature information pertinent to the implementation and operation of the processor on its respective platform.

**Note:** Throughout this document, the Intel® Atom<sup>™</sup> Processor D2000 series and N2000 Series processor is referred to as processor and Intel<sup>®</sup> NM10 Express Chipset is referred to as chipset.

The processor is built on 32-nanometer Hi-K process technology. The processor is designed for a two-chip platform as opposed to the traditional three-chip platforms (processor, GMCH, and ICH). The two-chip platform consists of a processor and the chipset and enables higher performance, lower cost, easier validation, and improved x-y footprint.

Included in this family of processors is an integrated memory controller (IMC), integrated graphics processing unit (GPU) and integrated I/O on a single silicon die. This single die solution is known as a monolithic processor.

#### 1.1 Intel® Atom<sup>™</sup> Processor D2000 Series and N2000 Series Features

The following list provides some of the key features on this processor:

- On die, primary 32kB, 4-way L1 instructions cache and 24kB, 6-way L1 write-back data cache

- Intel<sup>®</sup> Hyper-Threading Technology 2-threads per core except for D2500 no HT support

- 512-kB, 8-way ECC protected L2 cache per core processor

- Support for IA 32-bit

- Intel<sup>®</sup> Streaming SIMD Extensions 2 and 3 (SSE2 and SSE3) and Supplemental Streaming SIMD Extensions 3 (SSSE3) support

- Intel<sup>®</sup> 64 architecture

- Micro-FCBGA11 packaging technologies

- Thermal management support via  ${\rm Intel}^{\circledast}$  Thermal Monitor (TM1 & TM2) ELD TM1 only

- Supports C0 and C1 states only for D2000 series; C0-C4, C1E-C4E and Deep Power Down Technology (code named C6) state for N2000 series processor

- Execute Disable Bit support for enhanced security

## **1.2 System Memory Features**

- One channel of DDR3

- memory (consists of 64 data lines):

- Maximum of two SODIMMs per channel for D2000 series and N2800 Processor performance, containing single or double-sided SODIMM

- Maximum of one SODIMMs per channel for N2600 series Processor only, containing single or double-sided SODIMM.

- Memory DDR3 data transfer rates of 800 MT/s (6.4 GB/s) and 1066 MT/s (8.5 GB/s)

- Only non-ECC SODIMMs are supported

- Refreshed SKU of Next Generation Intel® Atom<sup>™</sup> Processor based Mobile Platform Processors support DDR3/DDR3L.

- Support Small Outline DIMMs Raw Cards RC-A (2Rx16), RC-B(1Rx8), RC-C (1Rx16) and RC-F (2Rx8) for DDR3. Support Small Outline DIMMs Raw Cards RC-B (1Rx8) and RC-F (2Rx8) for DDR3L.

- Does not support RC-D (2Rx16 dual die), and RC-E(2Rx16)

- No mixed Raw Card support.

- Support unbuffered SODIMMs

- Supports Memory Down Design with Raw Card Type B only

- I/O Voltage of 1.5 V for DDR3. I/O Voltage of 1.35 V for DDR3L.

- Max memory size by sku: N2600 series 2 GB; N2800, D2500 & D2700 series 4 GB

- Supports total memory size of 1 GB, 2 GB and 4 GB max

- Supports Max densities 1 Gbit, 2 Gbit for both x8 and x16 for DDR3

- DRAM Chip Data Width: x8 and x16

- Banks / DRAM Chip: 8

- Support up to 32 simultaneous open pages per channel (assuming 4 ranks of 8 devices)

- Support Partial Writes to memory using Data Mask signals (DM)

- Enhances Address Mapping

- Support DIMM page size of 1 KB and 2 KB

- Support data burst length of 8 and Burst Chopped of 4 for all memory configurations

- Support memory thermal management scheme to selectively manage reads and/or writes. Memory thermal management can be triggered by either on-die thermal sensor, or by preset limits. Management limits are determined by weighted sum of various commands that are scheduled on the memory interface.

### **1.3 Direct Media Interface Features**

- Compliant to Direct Media Interface (DMI)

- Support 2 lanes in each direction for N2000 series processor and 4 lanes in each direction for D2000 series, Gen1 (2.5 Gbps) per lane per direction, point-to-point DMI interface to Intel® NM10 Express Chipset or PCH respectively.

- The N2000 series processor can only work on boards that have a DMI x2 connection. It will not work on a board with a DMI x4 connection. While the D2000 series processor can only work on the boards have a DMI x4 connection.

- 100 MHz reference.

- Support 64 bit downstream address (only 36-bit addressable from CPU)

- Support APIC messaging support. Will send Intel-defined "End of Interrupt" broadcast message when initiated by CPU.

- Support messaging in both directions, including Intel-Vendor specific messages.

- Support Message Signal Interrupt (MSI) messages.

- Support Power Management state change messages.

- Support SMI, SCI and SERR error indication.

- Support PCI INTA interrupt from CHAP Counters device and Integrated Graphics.

- Support Intel® NM10 Express Chipset with on board hybrid AC-DC coupling solution.

- Support polarity inversion (However, NM10 does not support)

#### 1.4 Graphics Processing Unit Features

- Support Directx\*9 compliant Pixel Shader\* v3.0 and OGL 3.0

- 640 MHz (D2550, D2700 & N2800/N2850) and 400 MHz (D2500 & N2600/N2650) graphic core frequency

- 200 MHz render clock frequency

- Seven display planes, Display Plane A, B, Display Sprite C (can be connected to either pipes), Display OV (can be connected to either pipes), Cursor A, Cursor B, and VGA

- Two display pipes, Pipe A and B support the dual independent displays

- Max Pixel Clock: SC LVDS: 112 MHz, 18bpp (N2000 series) & 18bpp and 24bpp (D2000 series); DDI: 2x 4, 1.62GHz, 2.7GHz; VGA: up to 350MHz

- Display Ports: eDP/DP x4, HDMI, LVDS (single channel), CRT/DAC

- Embedded panel: eDP1.1 or LVDS

- External panel: DP1.1, HDMI1.3a, LVDS, CRT/DAC.

- Supports HDCP 1.3 & PAVP1.1c (D2550, D2700 & N2800/N2850 processor) for Bluray playback while HDCP is needed for High Definition playback in Intel® Atom<sup>™</sup> Processor D2000 and N2000 series

- PAVP: Collection of HW-based security mechanisms designed to provide a secure path for content from a media player application to the graphics hardware

- HDCP: Specification developed by Intel Corporation to protect digital entertainment content across the DVI interface

- Subsequently ported to HDMI and Display Port

- Supports HDMI 1.3a through SW lip-sync

- Supports NV12 data format

- 3x3 Panel Fitter shared by two pipes

- Support Intel HD Audio Codec

- Support Intel® Display Power Saving Technology (Intel® DPST) 4.0

- No Frame Buffer Compensation (FBC)

- No TVOut

#### Table 1-1. Summary of the Resolution of Graphic interface

| Interfaces       | Processor    | Max<br>Resolution | Remark                                   |

|------------------|--------------|-------------------|------------------------------------------|

| LVDS (Single Ch) | N2000 series | 1366 x 768        | 60 Hz; 18 bpps                           |

| LVD3 (Single Ch) | D2000 series | 1440 x 900        | 60 Hz; 18 & 24 bpps                      |

| eDP              | N2000 series | 1366 x 768        | 60 Hz                                    |

| eDr              | D2000 series | 1920 x 1080       | 60 Hz                                    |

| VGA (CRT/DAC)    | N2000 series | 1920 x 1200       | 60 Hz at 267 MHz Max                     |

|                  | D2000 series | 1920 x 1200       | 60 Hz at 355 MHz Max                     |

| DP               | N2000 series | 1600 x 1200       | 60 Hz with 4 lanes at 162 MHz link clock |

|                  | D2000 series | 2560 x 1600       | 60 Hz with 4 lanes at 270 MHz link clock |

| HDMI/ DVI        | N2000 series | 1920 x 1200       | 60 Hz; up to 165MHz                      |

|                  | D2000 series | 1920 x 1200       | 60 Hz; up to 165MHz                      |

#### 1.5 Video

- The Intel Atom Processor D2000 series and N2000 series supports full MPEG2 (VLD/ iDCT/MC), WMV, Fast video Composing, HW decode/ acceleration for MPEG4 Part 10 (AVC/H.264) & VC-1; 720p60, 1080i60, 1080p@24 up to 20 Mps

- MPEG4 part2 does not utilize Next Generation Intel® Atom<sup>™</sup> Processor based desktop platform H/W

- Hardware Decode assist for Flash Decode for Adobe 11.0 and newer versions

- D2550, D2700 and N2800/N2850 processor supports Blu-Ray\* 2.0 playback 1 x HD and 1 x SD streaming

- Video image Enhancement: Hue, Saturation, Brightness, Contrast (HSBC) adjust, Bob De-Interlacing

- Support two Streams of 1080p HD @ 267 MHz

## 1.6 Clocking

- Differential Host clock of 100 MHz (HPL\_CLKINP/HPL\_CLKINN).

- Memory clocks 100MHz differential for both DDR3-800 and DDR3-1066

- When running DDR3-800 or DDR3-1066, the 1x memory clocks is generated from internal Host PLL and the 2x memory clock is generated from Memory PLL

- The differential DMI clock of 100 MHz (EXP\_CLKINP/EXP\_CLKINN) generates the DMI core clock of 250 MHz.

- Display timings are generated from display PLLs that use a 96 MHz differential non-SSC for VGA only, and 100 MHz differential clock with SSC or non-SSC as reference.

- Host, Memory, DMI, Display PLLs and all associated internal clocks are disabled until PWROK is asserted.

- The Display core clock Frequency by Skus

#### Table 1-2. The Display core clock Frequency by Skus

| Display Core<br>Clock | D2500 | D2550/<br>D2700 | N2600 | N2800 | Remark |

|-----------------------|-------|-----------------|-------|-------|--------|

| Frequency/ MHz        | 355   | 355             | 200   | 267   |        |

• 27 MHz crystal is needed to resolve digital display quality concerns.

#### Table 1-3. 27 MHz Requirement Range

| Min/MHz | Nominal/<br>MHz | Max/MHz | Remark  |

|---------|-----------------|---------|---------|

| 26.9919 | 27              | 27.0081 | 300 ppm |

#### **1.7 Power Management**

- PC99 suspend to DRAM support ("STR", mapped to ACPI state S3)

- SMRAM space remapping to A0000h (128 kB)

- Support extended SMRAM space above 256 MB, additional 1MB TSEG from the base of graphics stolen memory (BSM) when enabled, and cacheable (cacheability controlled by CPU).

- ACPI Rev 1.0b compatible power management

- Support CPU states: C0 and C1 (for D2000 series); C0-C4, C1E-C4E, Deep Power Down Technology (code named C6)(for N2000 series)

- Support System states: S0, S3, S4 and S5

- Support CPU Thermal Management (TM1 & TM2) while D2000 series is TM1 only

## 1.7.1 Terminology

| Term                             | Description                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     |  |  |  |  |

|----------------------------------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--|--|--|--|

| BGA                              | Ball Grid Array                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 |  |  |  |  |

| BLT                              | Block Level Transfer                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            |  |  |  |  |

| CRT                              | Cathode Ray Tube                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                |  |  |  |  |

| DDR3                             | Third generation Double Data Rate SDRAM memory technology                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       |  |  |  |  |

| DDR3L                            | Low Voltage DDR3                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                |  |  |  |  |

| DMA                              | Direct Memory Access                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            |  |  |  |  |

| DMI                              | Direct Media Interface                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          |  |  |  |  |

| DTS                              | Digital Thermal Sensor                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          |  |  |  |  |

| ECC                              | Error Correction Code                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           |  |  |  |  |

| Execute Disable Bit              | The Execute Disable bit allows memory to be marked as executable or non-executable, when combined with a supporting operating system. If code attempts to run in non-executable memory the processor raises an error to the operating system. This feature can prevent some classes of viruses or worms that exploit buffer overrun vulnerabilities and can thus help improve the overall security of the system. Refer to the <i>Intel</i> <sup>®</sup> 64 and IA-32 Architectures Software Developer's Manuals for more detailed information. |  |  |  |  |

| Micro-FBGA                       | Micro Flip Chip Ball Grid Array                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 |  |  |  |  |

| (G)МСН                           | Legacy component - Graphics Memory Controller Hub. Platforms designed for the N2000 series and D2000 series do not use an (G)MCH.                                                                                                                                                                                                                                                                                                                                                                                                               |  |  |  |  |

| GPU                              | Graphics Processing Unit                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        |  |  |  |  |

| ІСН                              | The legacy I/O Controller Hub component that contains the main PCI interface, LPC interface, USB2, Serial ATA, and other I/O functions. It communicates with the legacy (G)MCH over a proprietary interconnect called DMI. Platforms designed for the Intel Atom Processor D2000 series and N2000 series do not use an ICH.                                                                                                                                                                                                                     |  |  |  |  |

| IMC                              | Integrated Memory Controller                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    |  |  |  |  |

| Intel <sup>®</sup> 64 Technology | 64-bit memory extensions to the IA-32 architecture.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             |  |  |  |  |

| LCD                              | Liquid Crystal Display                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          |  |  |  |  |

| LLC                              | Last Level Cache. The LLC is the shared cache amongst all processor execution cores                                                                                                                                                                                                                                                                                                                                                                                                                                                             |  |  |  |  |

| LVDS                             | Low Voltage Differential Signaling<br>A high speed, low power data transmission standard used for display<br>connections to LCD panels.                                                                                                                                                                                                                                                                                                                                                                                                         |  |  |  |  |

| МСР                              | Multi-Chip                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      |  |  |  |  |

| NCTF                             | Non-Critical to Function: NCTF locations are typically redundant ground or non-critical reserved, so the loss of the solder joint continuity at end of life conditions will not affect the overall product functionality.                                                                                                                                                                                                                                                                                                                       |  |  |  |  |

| Processor                        | The 64-bit, multi-core component                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                |  |  |  |  |

| Term               | Description                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           |

|--------------------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| Processor Core     | The term "processor core" refers to Si die itself which can contain multiple execution cores. Each execution core has an instruction cache, data cache, and 256-KB L2 cache. All execution cores share the L3 cache.                                                                                                                                                                                                                                                                                                                                  |

| Rank               | A unit of DRAM corresponding to four to eight devices in parallel, ignoring ECC. These devices are usually, but not always, mounted on a single side of a SO-DIMM.                                                                                                                                                                                                                                                                                                                                                                                    |

| SCI                | System Control Interrupt. Used in ACPI protocol.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      |

| SMT                | Simultaneous Multi-Threading                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          |

| Storage Conditions | A non-operational state. The processor may be installed in a platform,<br>in a tray, or loose. Processors may be sealed in packaging or exposed<br>to free air. Under these conditions, processor landings should not be<br>connected to any supply voltages, have any I/Os biased or receive any<br>clocks. Upon exposure to "free air" (i.e., unsealed packaging or a<br>device removed from packaging material) the processor must be<br>handled in accordance with moisture sensitivity labeling (MSL) as<br>indicated on the packaging material. |

| TAC                | Thermal Averaging Constant                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            |

| TDP                | Thermal Design Power                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  |

| ТОМ                | Top of Memory                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         |

| ТТМ                | Time-To-Market                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        |

| V <sub>CC</sub>    | Processor core power supply                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           |

| V <sub>SS</sub>    | Processor ground                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      |

| V <sub>CCGFX</sub> | Graphics core power supply                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            |

| V_SM               | DDR3 power rail                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       |

| VLD                | Variable Length Decoding                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              |

## 1.8 References

Material and concepts available in the following documents may be beneficial when reading this document:

| Document                                                                   | Document Number                                          |

|----------------------------------------------------------------------------|----------------------------------------------------------|

| Intel® 64 and IA-32 Architectures Software Developer's Manuals             |                                                          |

| Volume 1: Basic Architecture                                               | http://www.intel.com/                                    |

| Volume 2A: Instruction Set Reference, A-M                                  | content/www/us/en/<br>processors/architectures-          |

| Volume 2B: Instruction Set Reference, N-Z                                  | software-developer-                                      |

| Volume 3A: System Programming Guide                                        | manuals.html?wapkw=archite<br>ctures+software+developers |

| Volume 3B: System Programming Guide                                        | +manuals                                                 |

| Intel Atom Processor D2000 series and N2000 Series<br>Specification Update | 326140                                                   |

| Intel Atom Processor D2000 series and N2000 Series Datasheet Volume 2 of 2 | 326137                                                   |

## 1.9 System Block Diagram

#### 1.9.1 PHOLD limitation on Legacy Feature

PHOLD protocol is a mechanism for ISA to lock the system so that it can do a DMA. Hence, the Intel Atom Processor D2000 series and N2000 series does NOT support PHOLD protocol which impacts the devices behind LPC (ISA) Super I/O only (No LPC mastering is allowed). These will need to be connected via USB adaptor if required.

This will not impact other legacy devices such as serial port, keyboard/mouse as well as USB based peripheral. If one of these devices are connected to LPC and a PHOLD is requested, Intel Atom Processor D2000 series and N2000 series will drop the request, set an error bit, and the system will immediately hang.

## 2 Signal Description

This chapter describes the processor signals. They are arranged in functional groups according to their associated interface or category. The following notations are used to describe the signal type:

#### Table 2-4. Signal Type

| Notations | Signal Type                     |

|-----------|---------------------------------|

| I         | Input Pin                       |

| 0         | Output Pin                      |

| I/O       | Bi-directional Input/Output Pin |

The signal description also includes the type of buffer used for the particular signal.

#### Table 2-5. Signal Description Buffer Types

| Signal | Description                                                                                                                                                                                         |

|--------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| CMOS   | CMOS buffers. 1.05 V tolerant                                                                                                                                                                       |

| DMI    | Direct Media Interface signals. These signals are compatible with PCI Express 1.0 Signalling Environment AC Specifications but are DC coupled. The buffers is 1.05 V/1.08 V and not 3.3 V tolerant. |

| HVCMOS | High Voltage buffers. 3.3 V tolerant                                                                                                                                                                |

| DDR3   | DDR3 buffers: 1.5 V tolerant. When implementing DDR3L, the buffer is 1.35 V tolerant.                                                                                                               |

| GTL+   | Open Drain Gunning Transceiver Logic signaling technology. Refer to GTL+ I/O Specification fro complete details.                                                                                    |

| ТАР    | Test Access Port signal                                                                                                                                                                             |

| Analog | Analog reference or output. May be used as a threshold voltage or for buffer compensation                                                                                                           |

| Ref    | Voltage reference signal                                                                                                                                                                            |

| Asynch | This signal is asynchronous and has no timing relationship with any reference clock.                                                                                                                |

| LVDS   | Low Voltage Differential Signalling. A high speed, low power data transmission standard used for display connections to LCD panels.                                                                 |

## 2.1 CPU Legacy Signal

#### Table 2-6. CPU Legacy Signal (Sheet 1 of 2)

| Signal Name   | Description                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     | Direction | Туре                  |

|---------------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-----------|-----------------------|

| EXTBGREF      | External Band gap Reference. SOC and Core Debug feature.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        | Ι         | Core<br>Analog        |

| HV_GPIO_RCOMP | RCOMP for 3.3V GPIO pins: 50 ohm 1% PD to VSS.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  | N/A       | Analog                |

| MV_GPIO_RCOMP | RCOMP for DFX_GPIO_GRPx pins: 50 ohm 1% PD to VSS.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              | N/A       | Analog                |